网络工程师计算机硬件知识练习题八

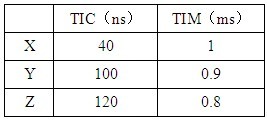

摘要:设有三个指令系统相同的处理机X、Y和Z,它们都有4K字节的高速缓冲存储器和32M字节的内存,但是其存取周期都不一样,如下表所示(TIC和TIM分别表示I处理机CACHE存取周期和主存存取周期);

【试题21】 设有三个指令系统相同的处理机X、Y和Z,它们都有4K字节的高速缓冲存储器和32M字节的内存,但是其存取周期都不一样,如下表所示(TIC和TIM分别表示I处理机CACHE存取周期和主存存取周期);

若某段程序,所需指令或数据在Cache中取到的概率为P=0.5,则处理机X的存储器平均存取周期为(③) ms。并假定指令执行时间与存储器的平均存取周期成正比。此时三个处理机执行该段程序由快到慢的顺序为(⑥) 。

若P=0.65时,则顺序为(⑤) 。

若P=0.8时,则顺序为(②) 。

若P=0.85时,则顺序为(①) 。〔1998年高级程序员考试〕

供选择的答案:

(50)①0.2 ②0.48 ③0.52 ④0.6

(51)~(54)

① X、Y、Z② X、Z、Y③ Y、X、Z④ Y、Z、X

⑤ Z、X、Y ⑥ Z、Y、X

【试题22】 在多级存储系统中,Cache处在CPU和主存之间,解决(②)问题。若Cache 和主存的存取时间分别为T1和T2,Cache 的命中率为H,则该计算机实际存取时间为(④)。当CPU向存储器执行读操作时,首先访问Cache ,若命中,则从Cache 中取出指令或数据,否则从主存中取出,送(③);当CPU向存储器执行写操作时,为了使Cache 内容和主存的内容保持一致,若采用(①)法,同时写入Cache 和主存。由于Cache 容量比主存容量小,当Cache 满时,但要执行把主存信息向Cache 写入时,就要淘汰Cache 中已有的信息,为了提高Cache 的命中率,采用一种(②)替换算法。〔1996年高级程序员〕

(55)①主存容量扩充 ②主存和CPU速度匹配

③多个请求源访问主存 ④BIOS存放

(56)①H T1+ T2②(1-H T1)+H T2 ③T2-H T1④H T1+(1-H)T2

(57)①Cache②CPU③Cache和CPU④Cache或CPU

(58)①写回②写通③映照④特征

(59)①LRU②FIFO③FILO④RANDOM

解析:

【试题21】根据公式:

平均存取周期=Cache存取周期×Cache命中率+主存存取周期×Cache失效率

=(0.5×0.04ms+0.5×1ms)

= 14.7 ns

依此类推,因为执行速度与存取周期(执行时间)成反比,在Cache命中率分别为0.5、0.65、0.8、0.85、条件下,三个处理机执行该段程序由快到慢的顺序分别为:Z、Y、X; Z、X、Y; X、 Z、Y;X、Y、Z。

【试题22】CACHE的主要功能是提供CPU与RAM间的速度匹配问题,存储器效率的计算公式为:H T1+(1-H)T2。为了提高Cache 的命中率,我们常采用LRU最近最少使用的替换算法。

编辑推荐:

2013年软考网络工程师考前试题及答案汇总

2013年计算机软考网络工程师基础知识讲义

延伸阅读

软考备考资料免费领取

去领取

- 0

- 7

- 6

专注在线职业教育24年

专注在线职业教育24年

扫描二维码

扫描二维码

扫描二维码

扫描二维码